Luồng tham chiếu mới dành cho TSMC N4PRF - công nghệ xử lý tần số vô tuyến (RF) FinFET 4 nanomet (nm) tiên tiến của nhà sản xuất bán dẫn hàng đầu thế giới. Luồng tham chiếu này dựa trên dòng giải pháp thiết kế tùy chỉnh Custom Design Family của Synopsys, cung cấp giải pháp thiết kế RF hoàn chỉnh cho khách hàng cần một môi trường thiết kế RF mở với độ chính xác dự báo và năng suất cao hơn.

Nhờ đó, các nhà thiết kế có thể lựa chọn các giải pháp chuyên ngành tốt nhất, bao gồm cả các các công cụ phân tích thiết kế mạch tích hợp tần số vô tuyến (RFIC) và các công cụ phân tích điện từ (EM) tương tác đã được xác nhận của Keysight cũng như các giải pháp mô hình hóa EM và xác minh toàn vẹn nguồn của Ansys.

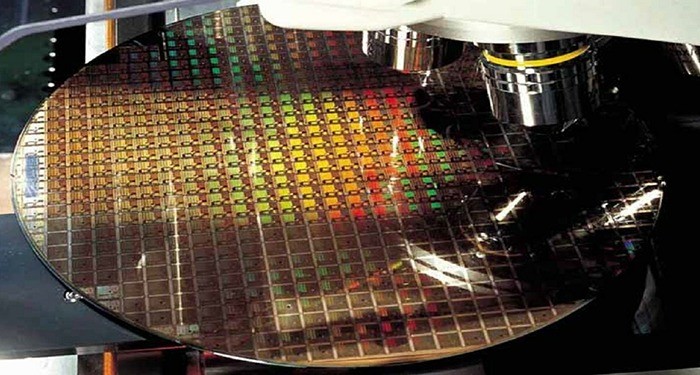

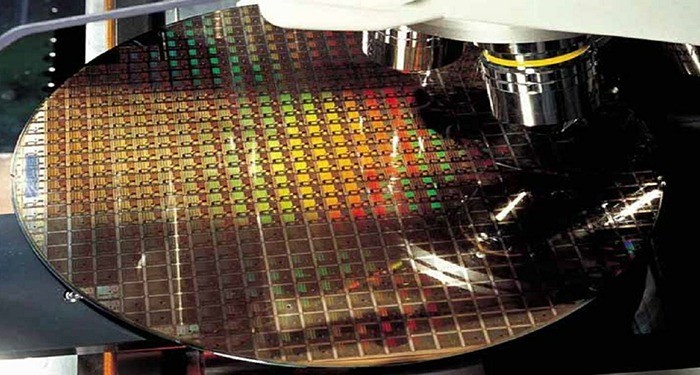

Nguồn: Everythingrf

Các hệ thống vô tuyến thế hệ tiếp theo có băng thông cao hơn, số lượng thiết bị được kết nối lớn hơn, độ trễ thấp hơn và vùng phủ sóng rộng hơn. Các mạch tích hợp RF sử dụng để truyền dữ liệu vô tuyến như trong các bộ thu phát và các thành phần giao diện người dùng RF có độ phức tạp thiết kế ngày càng cao. Tần số mạch cao hơn, kích thước nhỏ hơn và các hiệu ứng phức tạp phát sinh do bố trí linh kiện làm cho đặc tính vật lý của các thiết kế tốc độ cao trở nên rất phức tạp, đòi hỏi khả năng lập mô hình và mô phỏng chính xác và toàn diện hơn để đạt được hiệu suất cao nhất và độ tin cậy sản phẩm ổn định.

Luồng tham chiếu thiết kế TSMC N4PRF cải thiện thời gian quay vòng thiết kế và năng suất bố trí linh kiện trong môi trường thiết kế và bố trí linh kiện Synopsys Custom Compiler™ với tính năng xác nhận hợp chuẩn nghiêm ngặt bằng cách sử dụng các thành phần thiết kế trọng yếu bao gồm bộ khuếch đại nhiễu thấp (LNA) và bộ dao động điều khiển bằng điện áp LC tinh chỉnh (LC VCO).

Luồng tham chiếu bao gồm các công cụ hàng đầu thị trường, cho phép tổng hợp hiệu quả thiết bị thụ động, trích xuất mô hình EM, phân tích đặc tính dịch chuyển điện tử theo nhiệt độ của kim loại thiết bị và trích xuất sau bố trí linh kiện với việc xử lý chính xác các cấu trúc mạch dưới cuộn cảm (CUI).

Ngoài giải pháp Custom Compiler của Synopsys, luồng tham chiếu mở, hiện đại này còn có:

Khả năng mô phỏng mạch chính xác cho phê duyệt bằng các công cụ mô phỏng Synopsys PrimeSim™ và môi trường PrimeSim™ Reliability Environment, và các giải pháp xác minh và trích xuất vật lý cho phê duyệt với các công cụ Synopsys IC Validator™ và Synopsys StarRC™.

Giải pháp Totem™ của Ansys cung cấp chức năng xác minh đặc tính di chuyển điện tử theo nhiệt độ cho phê duyệt và phân tích tính toàn vẹn nguồn (EM/IR). Các giải pháp RaptorX™ và Exalto™ có chức năng lập mô hình điện từ, với các tính năng CUI độc đáo cho phép giảm đáng kể diện tích. Giải pháp VeloceRF™ cung cấp chức năng tổng hợp bố trí linh kiện silicon hoàn toàn tự động cho các thiết bị điện từ bao gồm cuộn cảm xoắn ốc đa lớp, balun/biến áp và đường truyền.

Giải pháp PathWave ADS RFPro của Keysight cho phép đồng mô phỏng và phân tích mạch EM tương tác, để nhanh chóng phát hiện và khắc phục sớm các hiệu ứng phát sinh từ bố trí linh kiện từ khi bắt đầu chu trình phát triển. Thiết kế PathWave RFIC (GoldenGate) hỗ trợ mô phỏng cân bằng tín hiệu ngay từ lúc bắt đầu quá trình thiết kế và xác minh chip.

Niels Faché, Phó Chủ tịch kiêm Tổng Giám đốc Keysight EDA: mở rộng hợp tác chiến lược về công nghệ với TSMC để nâng tầm thiết kế RF cho công nghệ RF 4nm tiên tiến của TSMC.

Niels Faché, Phó Chủ tịch kiêm Tổng Giám đốc Keysight EDA, cho biết: "Keysight, Synopsys và Ansys đã mở rộng hợp tác chiến lược về công nghệ với TSMC để nâng tầm thiết kế RF cho công nghệ RF 4nm tiên tiến của TSMC. Chúng tôi đã chứng kiến các nhà thiết kế RF gặp khó khăn khi sử dụng các giải pháp và luồng thế hệ cũ hơn, không dành cho các thiết kế hệ thống trên chip WiFi-7 và hệ thống phụ RF hiện nay. Mô phỏng và mô hình hóa chi tiết có độ chính xác đủ để phê duyệt thiết kế là những tính năng bắt buộc để xử lý các hiệu ứng mới phát sinh từ bố trí linh kiện. Các công cụ và quy trình công việc khác trên thị trường có thể không đáp ứng được các yêu cầu đúc mới nhất này và thường thiếu năng lực mô hình hóa các thiết kế analog hiện đại với hàng trăm cổng tín hiệu được ghép nối."

"Synopsys, Ansys và Keysight đã phát huy nhiều thập kỷ kinh nghiệm trong thiết kế analog, RF và thiết kế sử dụng nhiều mô hình vật lý tùy chỉnh để giảm rủi ro và rút ngắn thời gian thiết kế cho các khách hàng chung. Dự án hợp tác mới nhất của chúng tôi với Ansys và Keysight về quy trình tham chiếu thiết kế RF mới hỗ trợ quy trình N4P tiên tiến của TSMC cung cấp một quy trình mở và được tối ưu hóa, mang lại kết quả chất lượng vượt trội cho các hệ thống WiFi-7 tiên tiến." Sanjay Bali, Phó Chủ tịch Chiến lược và Quản lý sản phẩm thuộc Bộ phận EDA của Synopsys, cho biết.

John Lee, Phó Chủ tịch kiêm Tổng Giám đốc, bộ phận kinh doanh Điện tử, Bán dẫn và Quang học của Ansys, cho biết: "Môi trường đa vật lý đặt ra cho khách hàng của chúng tôi nhiều khó khăn thách thức mới liên quan đến tối ưu hóa công suất, diện tích, độ tin cậy và hiệu suất khi tần số RF chuyển lên dải tần sóng milimet và dải tần dưới THz. Để có thể thành công trong lần mô phỏng và phân tích thiết kế đầu tiên (first-pass), khách hàng nên áp dụng các giải pháp tốt nhất trong quy trình thiết kế. Chúng tôi cùng với Keysight và Synopsys đang hợp tác chặt chẽ với TSMC để đưa công nghệ lập mô hình điện từ và tính toàn vẹn nguồn hàng đầu trong trên thị trường vào quy trình thiết kế tùy chỉnh, đáp ứng nhu cầu của các nhà thiết kế mạch tốc độ cao."

Theo tạp chí Điện tử và Ứng dụng

Cập nhật tin tức công nghệ mới nhất tại fanpage Công nghệ & Cuộc sống

Nguồn tin: dientungaynay.vn

Tham gia bình luận